#### Design and Analysis of a Nondeterministic Parallel Breadth-First Search Algorithm

by

Tao Benjamin Schardl

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Engineering in Computer Science and Engineering

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2010

© Massachusetts Institute of Technology 2010. All rights reserved.

May 21, 2010

Certified by .....

Charles E. Leiserson Professor Thesis Supervisor

Accepted by .....

Dr. Christopher J. Terman Chairman, Department Committee on Graduate Theses

#### Design and Analysis of a Nondeterministic Parallel Breadth-First Search Algorithm

by

Tao Benjamin Schardl

Submitted to the Department of Electrical Engineering and Computer Science on May 21, 2010, in partial fulfillment of the requirements for the degree of Master of Engineering in Computer Science and Engineering

#### Abstract

I have developed a multithreaded implementation of breadth-first search (BFS) of a sparse graph using the Cilk++ extensions to C++. My PBFS program on a single processor runs as quickly as a standard C++ breadth-first search implementation. PBFS achieves high work-efficiency by using a novel implementation of a multiset data structure, called a "bag," in place of the FIFO queue usually employed in serial breadth-first search algorithms. For a variety of benchmark input graphs whose diameters are significantly smaller than the number of vertices — a condition met by many real-world graphs — PBFS demonstrates good speedup with the number of processing cores.

Since PBFS employs a nonconstant-time "reducer" — a "hyperobject" feature of Cilk++ — the work inherent in a PBFS execution depends nondeterministically on how the underlying work-stealing scheduler load-balances the computation. I provide a general method for analyzing nondeterministic programs that use reducers. PBFS also is nondeterministic in that it contains benign races which affect its performance but not its correctness. Fixing these races with mutual-exclusion locks slows down PBFS empirically, but it makes the algorithm amenable to analysis. In particular, I show that for a graph G = (V, E) with diameter D and bounded out-degree, this data-race-free version of PBFS algorithm runs in time  $O((V+E)/P+Dlg^3(V/D))$  on P processors, which means that it attains near-perfect linear speedup if  $P \ll (V+E)/Dlg^3(V/D)$ .

Some parts of this thesis represent joint work with Professor Charles E. Leiserson.

Thesis Supervisor: Charles E. Leiserson Title: Professor

#### Acknowledgments

Thanks to my advisor, Professor Charles E. Leiserson of MIT CSAIL, for his tremendous support and guidance in all aspects of this thesis work. Thanks to Aydın Buluç of University of California, Santa Barbara, who helped me obtain many of our benchmark tests. Pablo G. Halpern of Intel Corporation and Kevin M. Kelley of MIT CSAIL helped me debug PBFS's performance bugs. Matteo Frigo of Axis Semiconductor helped me weigh the pros and cons of reducers versus TLS. Thanks to the Cilk team at Intel and the Supertech Research Group at MIT CSAIL for their support. Thanks to all of my friends and family for their unending support and encouragement.

# Contents

| 1  | Introduction                                        | 11 |

|----|-----------------------------------------------------|----|

| 2  | Background on dynamic multithreading                | 15 |

| 3  | The PBFS algorithm                                  | 19 |

| 4  | The bag data structure                              | 23 |

| 5  | Implementation                                      | 29 |

| 6  | The dag model of computation                        | 35 |

| 7  | Reducers                                            | 43 |

| 8  | Analysis of programs with nonconstant-time reducers | 53 |

| 9  | Analysis of PBFS                                    | 69 |

| 10 | Conclusion                                          | 73 |

# **List of Figures**

| 1-1 | A standard serial breadth-first search algorithm.                          | 12 |

|-----|----------------------------------------------------------------------------|----|

| 1-2 | Characteristic performance of PBFS                                         | 14 |

| 2-1 | An example of the intuition behind reducers                                | 17 |

| 3-1 | The PBFS algorithm.                                                        | 20 |

| 3-2 | Modification to the PBFS algorithm to resolve the benign race              | 21 |

| 4-1 | Pseudocode for PENNANT-UNION                                               | 24 |

| 4-2 | Illustration of PENNANT-UNION operation.                                   | 24 |

| 4-3 | Pseudocode for PENNANT-SPLIT.                                              | 24 |

| 4-4 | An example bag.                                                            | 25 |

| 4-5 | Pseudocode for BAG-INSERT.                                                 | 25 |

| 4-6 | Table detailing the function $FA(x,y,z)$                                   | 26 |

| 4-7 | Pseduocode for BAG-UNION.                                                  | 26 |

| 4-8 | Pseudocode for BAG-SPLIT.                                                  | 27 |

| 5-1 | Performance results for breadth-first search.                              | 31 |

| 5-2 | Multicore Murphi application speedup                                       | 33 |

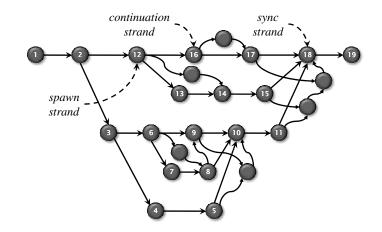

| 6-1 | A dag representation of a multithreaded execution.                         | 37 |

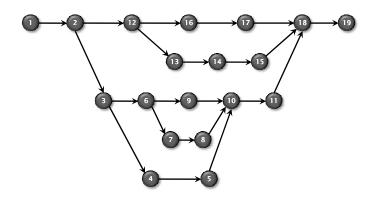

| 6-2 | A user dag representation of a multithreaded computation without reducers. | 38 |

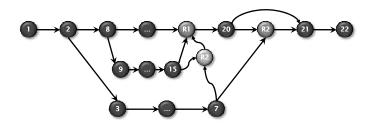

| 7-1 | A modified locking protocol for managing reducers                          | 46 |

| 7-2 | A dag representation of a computation with a REDUCE operation executed     |    |

|     | opportunistically.                                                         | 50 |

### Introduction

Algorithms to search a graph in a breadth-first manner have been studied for over 50 years. The first breadth-first search (BFS) algorithm was discovered by Moore [27] while studying the problem of finding paths through mazes. Lee [23] independently discovered the same algorithm in the context of routing wires on circuit boards. A variety of parallel BFS algorithms have since been explored [3,10,22,26,33,34]. Some of these parallel algorithms are *work efficient*, meaning that the total number of operations performed is the same to within a constant factor as that of a comparable serial algorithm. That constant factor, which we call the *work efficiency*, can be important in practice, but few if any papers actually measure work efficiency. In this thesis, we shall see a parallel BFS algorithm, called PBFS, whose performance scales linearly with the number of processors and for which the work efficiency is nearly 1, as measured by comparing its performance on benchmark graphs to the classical FIFO-queue algorithm [11, Section 22.2].

Given a graph G = (V, E) with vertex set V = V(G) and edge set E = E(G), the BFS problem is to compute for each vertex  $v \in V$  the distance *v.dist* that *v* lies from a distinguished *source* vertex  $v_0 \in V$ . We measure distance as the minimum number of edges on a path from  $v_0$  to *v* in *G*. For simplicity in the statement of results, we shall assume that *G* is connected and undirected, although the algorithms we shall explore apply equally as well to unconnected graphs, digraphs, and multigraphs.

Figure 1-1 gives a variant of the classical serial algorithm [11, Section 22.2] for computing BFS, which uses a FIFO queue as an auxiliary data structure. The FIFO can be

SERIAL-BFS  $(G, v_0)$ for each vertex  $u \in V(G) - \{v_0\}$ 1 2  $u.dist = \infty$ 3  $v_0.dist = 0$ 4  $Q = \{v_0\}$ 5 while  $Q \neq \emptyset$ 6 u = DEQUEUE(Q)7 for each  $v \in V(G)$  such that  $(u, v) \in E(G)$ 8 if v. dist ==  $\infty$ 9 v.dist = u.dist + 1ENQUEUE(Q, v)10

**Figure 1-1:** A standard serial breadth-first search algorithm operating on a graph *G* with source vertex  $v_0 \in V(G)$ . The algorithm employs a FIFO queue *Q* as an auxiliary data structure to compute for each  $v \in V(G)$  its distance *v*. *dist* from  $v_0$ .

implemented as a simple array with two pointers to the head and tail of the items in the queue. Enqueueing an item consists of incrementing the tail pointer and storing the item into the array at the pointer location. Dequeueing consists of removing the item referenced by the head pointer and incrementing the head pointer. Since these two operations take only  $\Theta(1)$  time, the running time of SERIAL-BFS is  $\Theta(V + E)$ . Moreover, the constants hidden by the asymptotic notation are small due to the extreme simplicity of the FIFO operations.

Although efficient, the FIFO queue Q is a major hindrance to parallelization of BFS. Parallelizing BFS while leaving the FIFO queue intact yields minimal parallelism for *sparse* graphs — those for which  $|E| \approx |V|$ . The reason is that if each ENQUEUE operation must be serialized, the *span*<sup>1</sup> of the computation — the longest serial chain of executed instructions in the computation — must have length  $\Omega(V)$ . Thus, a *work-efficient* algorithm — one that uses no more work than a comparable serial algorithm — can have *parallelism* — the ratio of work to span — at most O((V + E)/V) = O(1) if |E| = O(V).<sup>2</sup>

Replacing the FIFO queue with another data structure in order to parallelize BFS may compromise work efficiency, however, because FIFO's are so simple and fast. We have devised a multiset data structure called a *bag*, however, which supports insertion essentially

<sup>1</sup>Sometimes called *critical-path length* or *computational depth*.

$<sup>^{2}</sup>$ For convenience, we omit the notation for set cardinality within asymptotic notation.

as fast as a FIFO, even when constant factors are considered. In addition, bags can be split and unioned efficiently.

I have implemented a parallel BFS algorithm in Cilk++ [21,24]. The *PBFS* algorithm, which employs bags instead of a FIFO, uses the "reducer hyperobject" [15] feature of Cilk++. My implementation of PBFS runs comparably on a single processor to a good serial implementation of BFS. For a variety of benchmark graphs whose diameters are significantly smaller than the number of vertices — a common occurrence in practice — PBFS demonstrates high levels of parallelism and generally good speedup with the number of processing cores.

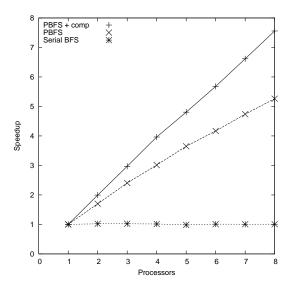

Figure 1-2 shows the typical speedup obtained for PBFS on a large benchmark graph, in this case, for a sparse matrix called Cage15 arising from DNA electrophoresis [32]. This graph has |V| = 5,154,859 vertices, |E| = 99,199,551 edges, and a diameter of D = 50. The code was run on an Intel Core i7 machine with eight 2.53 GHz processing cores, 12 GB of RAM, and two 8 MB L3-caches, each shared among 4 cores. As can be seen from the figure, although PBFS scales well initially, it attains a speedup of only about 5 on 8 cores, even though the parallelism in this graph is nearly 700. The figure graphs the impact of artificially increasing the *computational intensity* — the ratio of the number of CPU operations to the number of memory operations, suggesting that this low speedup is due to limitations of the memory system, rather than to the inherent parallelism in the algorithm.

PBFS is a nondeterministic program for two reasons. First, because the program employs a bag reducer which operates in nonconstant time, the asymptotic amount of work can vary from run to run depending upon how Cilk++'s work-stealing scheduler load-balances the computation. Second, for efficient implementation, PBFS contains a benign race condition, which can cause additional work to be generated nondeterministically. My theoretical analysis of PBFS bounds the additional work due to the bag reducer when the race condition is resolved using mutual-exclusion locks. Theoretically, on a graph *G* with vertex set V = V(G), edge set E = E(G), diameter *D*, and bounded out-degree, this "locking" version of PBFS performs BFS in  $O((V + E)/P + Dlg^3(V/D))$  time on *P* processors and exhibits effective parallelism  $\Omega((V + E)/Dlg^3(V/D))$ , which is considerable when  $D \ll V$ , even if the graph is sparse. Our method of analysis is general and can be applied to other programs

**Figure 1-2:** The performance of PBFS for the Cage15 graph showing speedup curves for serial BFS, PBFS, and a variant of PBFS where the computational intensity has been artificially enhanced and the speedup normalized.

that employ reducers. This thesis leaves it as an open question how to analyze the extra work when the race condition is left unresolved.

The remainder of this paper is divided as follows. First, we shall examine the basic PBFS algorithm and analyze it empirically. Chapter 2 provides background on dynamic multithreading. Chapter 3 descirbed the basic PBFS algorithm, and Chapter 4 describes the implementation of the bag data structure. Chapter 5 presents our empirical studies.

Second, we shall create a theoretical framework for analyzing programs with nonconstant time reducers, and apply this framework to analyze PBFS. Chapter 6 provides background on the theory of dynamic multithreading. Chapter 7 gives a formal model for reducer behavior, and Chapter 8 develops a theory for analyzing programs that use reducers. Chapter 9 emplys this theory to analyze the theoretical performance of PBFS.

Finally, Chapter 10 concludes with a discussion of thread-local storage as an alternative to reducers.

### **Background on dynamic multithreading**

This chapter overviews the key attributes of dynamic multithreading. The PBFS software is implemented in Cilk++ [15, 21, 24], which is a linguistic extension to C++ [30], but most of the vagaries of C++ are unnecessary for understanding the issues. Thus, I describe Cilk-like pseudocode, as is exemplified in [11, Ch. 27], which the reader should find more straightforward than real code to understand and which can be translated easily to Cilk++. In this chapter we shall review the pseudocode keywords for creating fork-join parallel programs. We shall also see the basic intuition behind the reducer hyperobject.

#### Multithreaded pseudocode

The linguistic model for multithreaded pseudocode in [11, Ch. 27] follows MIT Cilk [16, 31] and Cilk++ [21, 24]. It augments ordinary serial pseudocode with three keywords — **spawn**, **sync**, and **parallel** — of which **spawn** and **sync** are the more basic.

Parallel work is created when the keyword **spawn** precedes the invocation of a function. The semantics of spawning differ from a C or C++ function call only in that the parent *continuation* — the code that immediately follows the spawn — may execute in parallel with the spawned child, instead of waiting for the child to complete, as is normally done for a function call. A function cannot safely use the values returned by its children until it executes a **sync** statement, which suspends the function until all of its spawned children return. Every function syncs implicitly before it returns, precluding orphaning. Together, **spawn**

and **sync** allow programs containing fork-join parallelism to be expressed succinctly. The scheduler in the runtime system takes the responsibility of scheduling the spawned functions on the individual processor cores of the multicore computer and synchronizing their returns according to the fork-join logic provided by the **spawn** and **sync** keywords.

Loops can be parallelized by preceding an ordinary **for** with the keyword **parallel**, which indicates that all iterations of the loop may operate in parallel. Parallel loops do not require additional runtime support, but can be implemented by parallel divide-and-conquer recursion using **spawn** and **sync**.

Cilk++ provides a novel linguistic construct, called a *reducer hyperobject* [15], which allows concurrent updates to a shared variable or data structure to occur simultaneously without contention. A reducer is defined in terms of a binary associative **REDUCE** operator, such as sum, list concatenation, logical AND, etc. Updates to the hyperobject are accumulated in local *views*, which the Cilk++ runtime system combines automatically with "up-calls" to REDUCE when subcomputations join. As we shall see in Chapter 3, PBFS uses a reducer called a "bag," which implements an unordered set and supports fast unioning as its REDUCE operator.

Figure 2-1 illustrates the basic idea of a reducer. The example involves a series of additive updates to a variable x. When the code in Figure 2-1(a) is executed serially, the resulting value is x = 16. Figure 2-1(b) shows the same series of updates split between two "views" x and x' of the variable. These two views may be evaluated independently in parallel with an additional step to *reduce* the results at the end, as shown in Figure 2-1(b). As long as the values for the views x and x' are not inspected in the middle of the computation, the associativity of addition guarantees that the final result is deterministically x = 16. This series of updates could be split anywhere else along the way and yield the same final result, as demonstrated in Figure 2-1(c), where the computation is split across three views x, x', and x''. To encapsulate nondeterminism in this way, each of the views must be reduced with an associative REDUCE operator (addition for this example) and intermediate views must be initialized to the identity for REDUCE (0 for this example).

Cilk++'s reducer mechanism supports this kind of decomposition of update sequences automatically without requiring the programmer to manually create various views. When

| 1  | x = 10      | 1  | x = 10      | 1  | x = 10      |

|----|-------------|----|-------------|----|-------------|

| 2  | x++         | 2  | <i>x</i> ++ | 2  | <i>x</i> ++ |

| 3  | x += 3      | 3  | x += 3      | 3  | x += 3      |

| 4  | x += -2     | 4  | x += -2     |    | x' = 0      |

| 5  | x += 6      | 5  | x += 6      | 4  | x' += -2    |

| 6  | <i>x</i> —— |    | x' = 0      | 5  | x' += 6     |

| 7  | x += 4      | 6  | x'          | 6  | <i>x</i> ′  |

| 8  | x += 3      | 7  | x' += 4     |    | x'' = 0     |

| 9  | <i>x</i> ++ | 8  | x' += 3     | 7  | x'' += 4    |

| 10 | x += -9     | 9  | x'++        | 8  | x'' += 3    |

|    |             | 10 | x' += -9    | 9  | x'' + +     |

|    |             |    | x += x'     | 10 | x'' += -9   |

|    |             |    |             |    | x += x'     |

|    |             |    |             |    | x += x''    |

|    | (a)         |    | (b)         |    | (c)         |

**Figure 2-1:** The intuition behind reducers. (a) A series of additive updates performed on a variable *x*. (b) The same series of additive updates split between two "views" *x* and *x'*. The two update sequences can execute in parallel and are combined at the end. (c) Another valid splitting of these updates among the views *x*, *x'*, and *x''*.

a function spawns, the spawned child inherits the parent's view of the hyperobject. If the child returns before the continuation executes, the child can return the view and the chain of updates can continue. If the continuation begins executing before the child returns, however, the continuation receives a new view initialized to the identity for the associative REDUCE operator. Sometime at or before the **sync** that joins the spawned child with its parent, the two views are combined with REDUCE. If REDUCE is indeed associative, the result is the same as if all the updates had occurred serially. Indeed, if the program is run on one processor, the entire computation updates only a single view without ever invoking the REDUCE operator, in which case the behavior is virtually identical to a serial execution that uses an ordinary object instead of a hyperobject. We shall formalize reducers in Chapter 7.

### **The PBFS algorithm**

PBFS uses *layer synchronization* [3, 34] to parallelize breadth-first search of an input graph *G*. Let  $v_0 \in V(G)$  be the source vertex, and define *layer d* to be the set  $V_d \subseteq V(G)$  of vertices at distance *d* from  $v_0$ . Thus, we have  $V_0 = \{v_0\}$ . Each iteration processes layer *d* by checking all the neighbors of vertices in  $V_d$  for those that should be added to  $V_{d+1}$ .

PBFS implements layers using an unordered-set data structure, called a *bag*, which provides the following operations:

- bag = BAG-CREATE(): Create a new empty bag.

- BAG-INSERT (*bag*, *x*): Insert element *x* into *bag*.

- BAG-UNION(*bag*<sub>1</sub>, *bag*<sub>2</sub>): Move all the elements from *bag*<sub>2</sub> to *bag*<sub>1</sub>, and destroy *bag*<sub>2</sub>.

- $bag_2 = BAG-SPLIT(bag_1)$ : Remove half (to within some constant amount GRAIN-SIZE of granularity) of the elements from  $bag_1$ , and put them into a new bag  $bag_2$ .

As Chapter 4 shows, BAG-CREATE operates in O(1) time, and BAG-INSERT operates in O(1) amortized time. Both BAG-UNION and BAG-SPLIT operate in  $O(\lg n)$  time on bags with *n* elements.

Let us walk through the pseudocode for PBFS, which is shown in Figure 3-1. For the moment, ignore the **revert** and **reducer** keywords in lines 8 and 9.

After initialization, PBFS begins the **while** loop in line 7 which iteratively calls the auxiliary function PROCESS-LAYER to process layer d = 0, 1, ..., D, where D is the diameter of the input graph G. To process  $V_d = in-bag$ , PROCESS-LAYER uses parallel divide-and-

```

PBFS(G, v_0)

parallel for each vertex v \in V(G) - \{v_0\}

1

2

v.dist = \infty

3

v_0.dist = 0

4

d = 0

5 V_0 = \text{BAG-CREATE}()

BAG-INSERT(V_0, v_0)

6

7

while \negBAG-IS-EMPTY(V_d)

8

V_{d+1} = new reducer BAG-CREATE()

9

PROCESS-LAYER (revert V_d, V_{d+1}, d)

10

d = d + 1

```

PROCESS-LAYER (*in-bag*, *out-bag*, *d*)

```

11

if BAG-SIZE(in-bag) < GRAINSIZE

12

for each u \in in-bag

13

parallel for each v \in Adj[u]

if v. dist == \infty

14

15

v.dist = d+1

// benign race

16

BAG-INSERT (out-bag, v)

17

return

18

new-bag = BAG-SPLIT(in-bag)

spawn PROCESS-LAYER (new-bag, out-bag, d)

19

20

PROCESS-LAYER(in-bag, out-bag, d)

```

21 **sync**

**Figure 3-1:** The PBFS algorithm operating on a graph *G* with source vertex  $v_0 \in V(G)$ . PBFS uses the recursive parallel subroutine PROCESS-LAYER to process each layer. It contains a benign race in line 15.

conquer, producing  $V_{d+1} = out\text{-}bag$ . For the recursive case, line 18 splits *in*-bag, removing half its elements and placing them in *new*-bag. The two halves are processed recursively in parallel in lines 19–20.

This recursive decomposition continues until *in-bag* has fewer than GRAINSIZE elements, as tested for in line 11. Each vertex u in *in-bag* is extracted in line 12, and line 13 examines each of its edges (u, v) in parallel. If v has not yet been visited — v.dist is infinite (line 14) — then line 15 sets v.dist = d + 1 and line 16 inserts v into the level-(d + 1) bag. As an implementation detail, the destructive nature of the BAG-SPLIT routine makes it particularly convenient to maintain only two bags at a time, ignoring additional views set

| 15.1 | <b>if</b> Try-Lock $(v)$                     |

|------|----------------------------------------------|

| 15.2 | <b>if</b> <i>v</i> . <i>dist</i> == $\infty$ |

| 15.3 | v.dist = d+1                                 |

| 15.4 | BAG-INSERT( <i>out-bag</i> , <i>v</i> )      |

| 15.5 | Release-Lock $(v)$                           |

Figure 3-2: Modification to the PBFS algorithm to resolve the benign race.

up by the runtime system.

This description skirts over two subtleties that require discussion, both involving races.

First, the update of *v.dist* in line 15 creates a race, since two vertices *u* and *u'* may both be examining vertex *v* at the same time. They both check whether *v.dist* is infinite in line 14, discover that it is, and both proceed to update *v.dist*. Fortunately, this race is benign, meaning that it does not affect the correctness of the algorithm. Both *u* and *u'* set *v.dist* to the same value, and hence no inconsistency arises from both updating the location at the same time. They both go on to insert *v* into bag  $V_{d+1} = out-bag$  in line 16, which could induce another race. Putting that issue aside for the moment, notice that inserting multiple copies of *v* into  $V_{d+1}$  does not affect correctness, only performance for the extra work it will take when processing layer d+1, because *v* will be encountered multiple times. As we shall see in Chapter 5, the amount of extra work is small, because the race is rarely actualized.

Second, a race in line 16 occurs due to parallel insertions of vertices into  $V_{d+1} = out$ -bag. We employ the reducer functionality to avoid the race by making  $V_{d+1}$  a bag reducer, where BAG-UNION is the associative operation required by the reducer mechanism. The identity for BAG-UNION — an empty bag — is created by BAG-CREATE. In the common case, line 16 simply inserts v into the local view, which, as we shall see in Chapter 4, is as efficient as pushing v onto a FIFO, as is done by serial BFS.

Unfortunately, we are not able to analyze PBFS due to unstructured nondeterminism created by the benign race, but we can analyze a version where the race is resolved using a mutual-exclusion lock. The locking version involves replacing lines 15 and 16 with the code in Figure 3-2. In the code, the call TRY-LOCK (v) in line 15.1 attempts to acquire a

lock on the vertex v. If it is successful, we proceed to execute lines 15.2–15.5. Otherwise, we can abandon the attempt, because we know that some other processor has succeeded, which then sets v.dist = d + 1 regardless. Thus, there is no contention on v's lock, because no processor ever waits for another, and processing an edge (u, v) always takes constant time. The apparently redundant lines 14 and 15.2 avoid the overhead of lock acquisition when v.dist has already been set.

### The bag data structure

This chapter describes the bag data structure for implementing a dynamic unordered set. We first examine an auxiliary data structure called a "pennant." We then see how bags can be implemented using pennants, and we provide algorithms for BAG-CREATE, BAG-INSERT, BAG-UNION, and BAG-SPLIT. Finally, we consider some optimizations of this structure that PBFS employs.

#### Pennants

A *pennant* is a tree of  $2^k$  nodes, where k is a nonnegative integer. Each node x in this tree contains two pointers x.*left* and x.*right* to its children. The root of the tree has only a left child, which is a complete binary tree of the remaining elements.

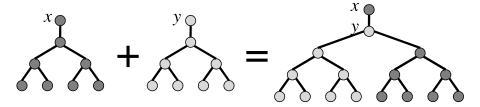

Two pennants *x* and *y* of size  $2^k$  can be combined to form a pennant of size  $2^{k+1}$  in O(1) time using the PENNANT-UNION function described in Figure 4-1, which is illustrated in Figure 4-2.

The function PENNANT-SPLIT, whose pseudocode is given in Figure 4-3, performs the inverse operation of PENNANT-UNION in O(1) time. The PENNANT-SPLIT function assumes that the input pennant *x* contains at least 2 elements. After this function, each of the pennants *x* and *y* contain half of the elements.

**PENNANT-UNION** (x, y)

- 1 y.right = x.left

- 2 x.left = y

- 3 return x

Figure 4-1: Pseudocode for PENNANT-UNION

**Figure 4-2:** Two pennants, each of size  $2^k$ , can be unioned in constant time to form a pennant of size  $2^{k+1}$ .

PENNANT-SPLIT (x)y = x.leftx.left = y.righty.right = NULL**return** y

Figure 4-3: Pseudocode for PENNANT-SPLIT.

#### Bags

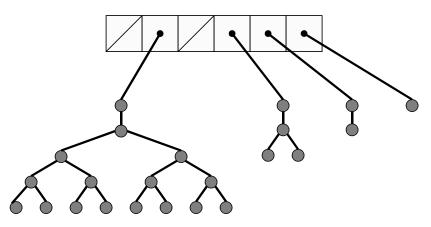

A *bag* is a collection of pennants, no two of which have the same size. PBFS represents a bag *S* using a fixed-size array S[0..r], called the *backbone*, where  $2^{r+1}$  exceeds the maximum number of elements ever stored in a bag. Each entry S[k] in the backbone contains either a null pointer or a pointer to a pennant of size  $2^k$ . Figure 4-4 illustrates a bag containing 23 elements. The function BAG-CREATE allocates space for a fixed-size backbone of null pointers, which takes  $\Theta(r)$  time. This bound can be improved to O(1) by keeping track of the largest nonempty index in the backbone.

The BAG-INSERT function employs an algorithm similar to that of incrementing a binary counter. To implement BAG-INSERT, we first package the given element as a pennant x of size 1. We then insert x into bag S using the method shown in Figure 4-5.

**Figure 4-4:** A bag with  $23 = 010111_2$  elements.

BAG-INSERT (S, x)1 k = 02 while  $S[k] \neq \text{NULL}$ 3 x = PENNANT-UNION(S[k], x)4 S[k++] = NULL5 S[k] = x

Figure 4-5: Pseudocode for BAG-INSERT. This function assumes the input pennant x has unit size.

The analysis of BAG-INSERT mirrors the analysis for incrementing a binary counter [11, Ch. 17]. Since every PENNANT-UNION operation takes constant time, BAG-INSERT takes O(1) amortized time and  $O(\lg n)$  worst-case time to insert into a bag of n elements.

The BAG-UNION function uses an algorithm similar to ripple-carry addition of two binary counters. To implement BAG-UNION, we first examine the process of unioning three pennants into two pennants, which operates like a full adder. Given three pennants x, y, and z, where each either has size  $2^k$  or is empty, we can merge them to produce a pair of pennants (s,c), where s has size  $2^k$  or is empty, and c has size  $2^{k+1}$  or is empty. The table in Figure 4-6 details the full-adder function FA(x,y,z) in which (s,c) is computed from (x,y,z). Using this full-adder function, BAG-UNION can be implemented as shown in Figure 4-7.

Because every PENNANT-UNION operation takes constant time, computing the value of FA(x, y, z) also takes constant time. To compute all entries in the backbone of the resulting

| X | у | Z. | S    | С                             |

|---|---|----|------|-------------------------------|

| 0 | 0 | 0  | NULL | NULL                          |

| 1 | 0 | 0  | х    | NULL                          |

| 0 | 1 | 0  | У    | NULL                          |

| 0 | 0 | 1  | Z.   | NULL                          |

| 1 | 1 | 0  | NULL | <b>PENNANT-UNION</b> $(x, y)$ |

| 1 | 0 | 1  | NULL | <b>PENNANT-UNION</b> $(x, z)$ |

| 0 | 1 | 1  | NULL | PENNANT-UNION $(y, z)$        |

| 1 | 1 | 1  | x    | PENNANT-UNION $(y, z)$        |

**Figure 4-6:** Table detailing the function FA(x,y,z). This function takes three input pennants *x*, *y*, and *z*, each of which either has size  $2^k$  or is empty, and merges them to produce a pair of pennants (s, c), where *s* has size  $2^k$  or is empty, and *c* has size  $2^{k+1}$  or is empty. A 0 in the left-hand-side of the table designates an empty pennant, while a 1 designates a pennant with size  $2^k$ .

BAG-UNION  $(S_1, S_2)$ y =NULL // The "carry" bit. **for** k = 0 **to** r $(S_1[k], y) =$ FA $(S_1[k], S_2[k], y)$

**Figure 4-7:** Pseudocode for BAG-UNION. This function uses the function FA(x,y,z) detailed in Figure 4-6 as a subroutine.

bag takes  $\Theta(r)$  time. This algorithm can be improved to  $\Theta(\lg n)$ , where *n* is the number of elements in the smaller of the two bags, by maintaining the largest nonempty index of the backbone of each bag and unioning the bag with the smaller such index into the one with the larger.

The BAG-SPLIT function is shown in Figure 4-8. This function operates like an arithmetic right shift to divide the elements in one bag evenly between two bags.

Because PENNANT-SPLIT takes constant time, each loop iteration in BAG-SPLIT takes constant time. Consequently, the asymptotic runtime of BAG-SPLIT is O(r). This algorithm can be improved to  $\Theta(\lg n)$ , where *n* is the number of elements in the input bag, by maintaining the largest nonempty index of the backbone of each bag and iterating only up

to this index.

```

BAG-SPLIT(S_1)

1 S_2 = BAG-CREATE()

2 y = S_1[0]

3

S_1[0] = \text{NULL}

4

for k = 1 to r

5

if S_1[k] \neq \text{NULL}

S_2[k-1] = \text{Pennant-Split}(S_1[k])

6

7

S_1[k-1] = S_1[k]

8

S_1[k] = \text{NULL}

9

if y \neq \text{NULL}

10

BAG-INSERT (S_1, y)

11

return S<sub>2</sub>

```

Figure 4-8: Pseudocode for BAG-SPLIT.

#### Optimization

To improve the constant in the performance of BAG-INSERT, we made some simple but important modifications to pennants and bags, which do not affect the asymptotic behavior of the algorithm. First, in addition to its two pointers, every pennant node in the bag stores a constant-size array of GRAINSIZE elements, all of which are guaranteed to be valid, rather than just a single element. My PBFS software implementation the value GRAINSIZE = 128. Second, in addition to the backbone, the bag itself maintains an additional pennant node of size GRAINSIZE called the *hopper*, which it fills gradually. The impact of these modifications on the bag operations is as follows.

First, BAG-CREATE must allocate additional space for the hopper. This overhead is small and is done only once per bag.

Second, BAG-INSERT first attempts to insert the element into the hopper. If the hopper is full, then it inserts the hopper into the backbone of the data structure and allocates a new hopper into which it inserts the element. This optimization does not change the asymptotic runtime analysis of BAG-INSERT, but the code runs much faster. In the common case, BAG-INSERT simply inserts the element into the hopper with code nearly identical to insert-ing an element into a FIFO. Only once in every GRAINSIZE insertions does a BAG-INSERT trigger the insertion of the now full hopper into the backbone of the data structure.

Third, when unioning two bags  $S_1$  and  $S_2$ , BAG-UNION first determines which bag has the less full hopper. Assuming that it is  $S_1$ , the modified implementation copies the elements of  $S_1$ 's hopper into  $S_2$ 's hopper until it is full or  $S_1$ 's hopper runs out of elements. If it runs out of elements in  $S_1$  to copy, BAG-UNION proceeds to merge the two bags as usual and uses  $S_2$ 's hopper as the hopper for the resulting bag. If it fills  $S_2$ 's hopper, however, line 1 of BAG-UNION sets y to  $S_2$ 's hopper, and  $S_1$ 's hopper, now containing fewer elements, forms the hopper for the resulting bag. Afterward, BAG-UNION proceeds as usual.

Finally, rather than storing  $S_1[0]$  into y in line 2 of BAG-SPLIT for later insertion, BAG-SPLIT sets the hopper of  $S_2$  to be the pennant node in  $S_1[0]$  before proceeding as usual.

### Implementation

I implemented optimized versions of both the PBFS algorithm in Cilk++ and a FIFObased serial BFS algorithm in C++. This chapter compares their performance on a suite of benchmark graphs. Figure 5-1 summarizes the results.

#### **Implementation and Testing**

My implementation of PBFS differs from the abstract algorithm in some notable ways. First, this implementation of PBFS does not use locks to resolve the benign races described in Chapter 3. Second, this implementation of PBFS does not use the BAG-SPLIT routine described in Chapter 4. Instead, this implementation uses a "lop" operation to traverse the bag. It repeatedly divides the bag into two approximately equal halves by lopping off the most significant pennant from the bag. After each lop, the removed pennant is traversed using a standard parallel tree walk. Third, this implementation assumes that all vertices have bounded out-degree, and indeed most of the vertices in our benchmark graphs have relatively small degree. Finally, this implementation of PBFS sets GRAINSIZE = 128, which seems to perform well in practice. The FIFO-based serial BFS uses an array and two pointers to implement the FIFO queue in the simplest way possible. This array was sized to the number of vertices in the input graph.

These implementations were tested on eight benchmark graphs, as shown in Figure 5-1. Kkt\_power, Cage14, Cage15, Freescale1, Wikipedia (as of February 6, 2007), and Nlp-

kkt160 are all from the University of Florida sparse-matrix collection [12]. Grid3D200 is a 7-point finite difference mesh generated using the Matlab Mesh Partitioning and Graph Separator Toolbox [17]. The RMat23 matrix [25], which models scale-free graphs, was generated by using repeated Kronecker products [2]. Parameters A = 0.7, B = C = D = 0.1for RMat23 were chosen in order to generate skewed matrices. These implementations store these graphs in a compressed-sparse-rows (CSR) format in main memory.

#### Results

I ran these tests on an Intel Core i7 quad-core machine with a total of eight 2.53-GHz processing cores (hyperthreading disabled), 12 GB of DRAM, two 8-MB L3-caches each shared between 4 cores, and private L2- and L1-caches with 256 KB and 32 KB, respectively. Figure 5-1 presents the performance of PBFS on eight different benchmark graphs. (The parallelism was computed using the Cilkview tool [19] and does not take into account effects from reducers.) As can be seen in Figure 5-1, PBFS performs well on these benchmark graphs. For five of the eight benchmark graphs, PBFS is as fast or faster than serial BFS. Moreover, on the remaining three benchmarks, PBFS is at most 15% slower than serial BFS.

Figure 5-1 shows that PBFS runs faster than a FIFO-based serial BFS on several benchmark graphs. This performance advantage may be due to how PBFS uses memory. Whereas the serial BFS performs a single linear scan through an array as it processes its queue, PBFS is constantly allocating and deallocating fixed-size chunks of memory for the bag. Because these chunks do not change in size from allocation to allocation, the memory manager incurs little work to perform these allocations. Perhaps more importantly, PBFS can reuse previously allocated chunks frequently, making it more cache-friendly. This improvement due to memory reuse is also apparent in some serial BFS implementations that use two queues instead of one.

Although PBFS generally performs well on these benchmarks, I explored why it was only attaining a speedup of 5 or 6 on 8 processor cores. Inadequate parallelism is not the answer, as most of the benchmarks have parallelism over 100. My studies indicate that the

| Name                   |                 | V               | Work           | SERIAL-BFS $T_1$ |

|------------------------|-----------------|-----------------|----------------|------------------|

| Description            | Spy Plot        | E               | Span           | PBFS $T_1$       |

|                        | <i>Spy Fibi</i> | D               | Parallelism    | PBFS $T_1/T_8$   |

|                        |                 |                 |                |                  |

| Kkt_power              |                 | 2.05M           | 241M           | 0.511            |

| Optimal power flow,    |                 | 12.76M          | 2.3M           | 0.360            |

| nonlinear opt.         |                 | 31              | 104.09         | 6.102            |

| Freescale1             |                 | 2 4214          | 24014          | 0.295            |

| Circuit simulation     |                 | 3.43M           | 349M           | 0.285            |

| Circuit simulation     |                 | 17.1M           | 2.3M           | 0.319            |

|                        |                 | 128             | 153.06         | 5.145            |

| Cage14                 |                 | 1.51M           | 390M           | 0.267            |

| DNA electrophoresis    |                 | 27.1M           | 1.6M           | 0.283            |

| DIA electrophotesis    |                 | 43              | 246.35         | 5.442            |

|                        |                 | 43              | 240.33         | 5.442            |

| Wikipedia              |                 | 2.4M            | 606M           | 0.918            |

| Links between          |                 | 41.9M           | 3.4M           | 0.738            |

| Wikipedia pages        |                 | 460             | 179.02         | 6.833            |

|                        |                 |                 |                |                  |

| Grid3D200              |                 | 8M              | 1,009M         | 1.469            |

| 3D 7-point             |                 | 55.8M           | 12.7M          | 1.098            |

| finite-diff mesh       |                 | 598             | 79.27          | 4.902            |

|                        |                 |                 |                |                  |

| RMat23                 |                 | 2.3M            | 1,049M         | 1.107            |

| Scale-free             |                 | 77.9M           | 11.3M          | 0.924            |

| graph model            |                 | 8               | 93.22          | 6.794            |

| ~                      |                 |                 |                |                  |

| Cage15                 |                 | 5.15M           | 1,410M         | 1.099            |

| DNA electrophoresis    |                 | 99.2M           | 2.1M           | 1.163            |

|                        |                 | 50              | 675.22         | 5.486            |

| Ninkkt160              |                 | O DENA          | 2 0601         | 1 296            |

| Nlpkkt160              |                 | 8.35M<br>225.4M | 3,060M<br>9.2M | 1.286            |

| Nonlinear optimization |                 |                 |                | 1.463            |

|                        |                 | 163             | 331.57         | 6.096            |

**Figure 5-1:** Performance results for breadth-first search. The vertex and edge counts listed correspond to the number of vertices and edges evaluated by SERIAL-BFS. The work and span are measured in instructions. All runtimes are measured in seconds.

multicore processor's memory system may be hurting performance in two ways.

First, the memory bandwidth of the system seems to limit performance for several of these graphs. For Wikipedia and Cage14, when we run 8 independent instances of PBFS serially on the 8 processing cores of our machine simultaneously, the total runtime is at least 20% worse than the expected  $8T_1$ . This experiment suggests that the system's available memory bandwidth limits the performance of the parallel execution of PBFS.

Second, for several of these graphs, it appears that contention from true and false sharing on the distance array constrains the speedups. Placing each location in the distance array on a different cache line tends to increase the speedups somewhat, although it slows down overall performance due to the loss of spatial locality. I attempted to modify PBFS to mitigate contention by randomly permuting or rotating each adjacency list. Although these approaches improve speedups, they slow down overall performance due to loss of locality. Thus, despite its somewhat lower relative speedup numbers, the unadulterated PBFS seems to yield the best overall performance.

PBFS obtains good performance despite the benign race which induces redundant work. On none of these benchmarks does PBFS examine more than 1% of the vertices and edges redundantly. Using a mutex lock on each vertex to resolve the benign race costs a substantial overhead in performance, typically slowing down PBFS by more than a factor of 2.

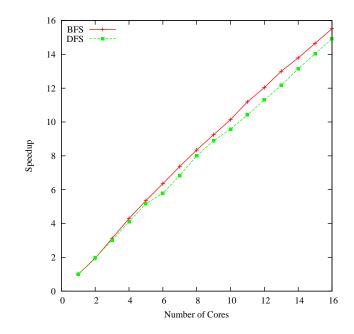

Yuxiong He [20], formerly of Cilk Arts and Intel Corporation, used PBFS to parallelize the Murphi model-checking tool [13]. Murphi is a popular tool for verifying finite-state machines and is widely used in cache-coherence algorithms and protocol design, link-level protocol design, executable memory-model analysis, and analysis of cryptographic and security-related protocols. As can be seen in Figure 5-2, a parallel Murphi using PBFS scales well, even outperforming a version based on parallel depth-first search and attaining the relatively large speedup of 15.5 times on 16 cores.

**Figure 5-2:** Multicore Murphi application speedup on a 16-core AMD processor [20]. Even though the DFS implementation uses a parallel depth-first search for which Cilk++ is particularly well suited, the BFS implementation, which uses the PBFS library, outperforms it.

### The dag model of computation

This chapter overviews the theoretical model of multithreaded computation. We shall see how a multithreaded program execution can be modeled theoretically as a dag using the framework of Blumofe and Leiserson [7], and we shall make some assumptions about the runtime environment. We shall derive a "user dag" from the dag model of computation to facilitate measuring the performance of a program with no reducers. We shall also define deterministic and nondeterministic computations. Chapter 7 describes how to extend this model to account for reducer hyperobjects.

#### The dag model

We adopt the dag model for multithreading similar to the one introduced by Blumofe and Leiserson [7]. This model was designed to model the execution of a multithreaded program with spawns and syncs. Although we incorporate instructions executed to manage reducers in this model, this model does not accurately represent the effect of reducers on the running time of the computation. We extend this model in Chapter 7 to account for the cost of dealing with reducers.

The dag model views the executed computation resulting from the running of a multithreaded program<sup>1</sup> as a *dag (directed acyclic graph)* A, where the vertex set V(A) consists of *strands* — sequences of serially executed instructions containing no parallel control —

<sup>&</sup>lt;sup>1</sup>When I refer to the running of a program, you should generally assume that I mean "on a given input."

and the edge set E(A) represents dependencies between strands. Specifically, V(A) contains all strands of two different types:

- User strands arising from the execution of code explicitly invoked by the programmer. We denote the set of strands of this type with  $V_{v}$ .

- *Runtime strands* arising from the execution of code run implicitly by the runtime system to create and reduce views of a reducer. We shall denote these runtime strands as  $V_1 \cup V_p$  in Chapter 7, which discusses these strands in more detail.

The edge set E(A) contains edges representing two types of dependencies: parallel-control dependencies and scheduling dependencies.

The *parallel-control dependencies*<sup>2</sup> E(A), denoted  $E_{\chi}$ , represent the dependencies that are described by **spawn** and **sync** statements in the code of the multithreaded program. A strand that has 2 outgoing control dependencies is a *spawn strand*, and a strand that resumes the caller after a spawn is called a *continuation strand*. A strand with at least 2 incoming control dependencies is a *sync strand*. We assume that no continuation strand is also a sync strand. We do not represent any control dependencies on runtime strands.

The scheduling dependencies in E(A), denoted  $E_{\sigma}$ , may be understood in terms of a schedule for A. A *schedule* of a computation A on a P-processor computer is a mapping  $C : V(A) \rightarrow \{0, 1, \dots, P-1\} \times \mathbb{N}$  where, for each strand  $u \in V(A)$ , if  $C(u) = (w_u, t_u)$  then worker  $w_u$  begins executing u at time step  $t_u$ . A scheduler creates a schedule for A's execution such that all scheduling dependencies are obeyed, where, for two strands  $u, v \in V(A)$ , a *scheduling dependency*  $(u, v) \in E_{\sigma}$  from u to v exists if v cannot legally execute before u has completed execution. For simplicity, we only consider a minimal set of scheduling dependencies, meaning that if  $(u, v) \in E_{\sigma}$ , then there does not exist a strand  $w \in V(A)$  such that  $(u, w) \in E_{\sigma}$  and  $(w, v) \in E_{\sigma}$ . This set  $E_{\sigma}$  of scheduling dependencies is included in the edge set E(A). If a strand u depends on every strand in a set  $\{v_1, v_2, \dots, v_k\} \subseteq V(A)$ , we say that the last strand in  $\{v_1, v_2, \dots, v_k\}$  to finish executing *enables* u.

We will often want to examine precedence relations between strands in V(A) with respect to only one edge set. We therefore define two precedence operators,  $\succ_{\chi}$  and  $\succ_{\sigma}$  as

<sup>&</sup>lt;sup>2</sup>We shall also refer to these dependencies simply as *control dependencies*.

**Figure 6-1:** A dag representation of a multithreaded execution. Each vertex represents a strand. Straight edges represent parallel-control dependencies between strands, while curved edges represent scheduling dependencies between strands. For visual simplicity, only scheduling dependencies that differ from parallel-control dependencies are shown. Vertices with no number depict strands executed implicitly by the runtime system to manage reducers.

follows. For two strands  $u, v \in V(A)$ , we have  $u \succ_{\chi} v$  in *A* if *u* precedes *v* in *A* according to only the edges in  $E_{\chi}$ . Similarly, we have  $u \succ_{\sigma} v$  in *A* if *u* precedes *v* in *A* according to only the edges in  $E_{\sigma}$ .

Although the scheduling dependencies are more restrictive than the parallel-control dependencies, they are related to the parallel-control dependencies by the following invariant:

**Invariant 1.** For two strands  $u, v \in V(A)$ , we have  $u \succ_{\chi} v \rightarrow u \succ_{\sigma} v$ .

For two strands  $u, v \in V(A)$ , we have  $u \succ_{\chi} v \to v \not\succeq_{\chi} u$ , and we have  $u \succ_{\sigma} v \to v \not\succeq_{\sigma} u$ . Together with Invariant 1, these implications guarantee that *A* is indeed a dag.

Figure 6-1 illustrates such a dag, which can be viewed as a parallel program "trace," in that it involves executed instructions as opposed to source instructions. A strand can be as small as a single instruction, or it can represent a longer computation. We shall assume that strands respect function boundaries, meaning that calling or spawning a function terminates a strand, as does returning from a function. Thus, each strand belongs to exactly one function instantiation.

Generally, we shall dice a chain of serially executed instructions into strands in a manner that is convenient for the computation we are modeling. The *length* of a strand is the time it takes for a processor to execute all its instructions. For simplicity, we shall assume

**Figure 6-2:** A user dag representation of a multithreaded computation without reducers. Each vertex represents a strand, and edges represent parallel-control dependencies between strands.

that programs execute on an *ideal parallel computer*, where each instruction takes unit time to execute, there is ample memory bandwidth, there are no cache effects, etc.

For convenience we derive two distinct dags from a computation A.

First, to simplify the task of bounding the performance of a computation A with no reducers, we derive a *user dag* User(A) from A by setting  $V(\text{User}(A)) = V_{\upsilon}$  and setting  $E(\text{User}(A)) = E_{\chi}$ . Figure 6-2 shows an example user dag for a computation containing no reducers. The convenience of the user dag is motivated by the following two facts about the performance of A. First, Blumofe and Leiserson prove in [7] that the performance of A may be bounded by only on the control dependencies in E(A). Second, since A does not contain reducers, then we have  $V(A) = V_{\upsilon}$ .

The second we derive is called a *scheduling dag* Sched(*A*). We derive Sched(*A*) from a computation *A* by setting V(Sched(A)) = V(A) and setting  $E(\text{Sched}(A)) = E_{\sigma}$ . We shall use the scheduling dag in Chapter 8 in order to construct a "delay-sequence" argument on computations that use reducers.

### **Determinacy**

We say that a dynamic multithreaded program is *deterministic* (on a given input) if every memory location is updated with the same sequence of values in every execution. Otherwise, the program is *nondeterministic*. A deterministic program always behaves the same, no matter how the program is scheduled. Two different memory locations may be updated in different orders, but each location always sees the same sequence of updates. Whereas a

nondeterministic program may produce different dags, i.e., behave differently, a deterministic program always produces the same dag.

### Work and span

The dag model admits two natural measures of performance which can be used to provide important bounds [6, 8, 14, 18] on performance and speedup. The *work* of a dag *A*, denoted by Work(*A*), is the sum of the lengths of all of the strands in V(A). For a computation that does not contain reducers, this equals the sum of the lengths of all strands in V(User(A)). For example, consider the user dag of a reducer-free computation modeled in Figure 6-2. Assuming for simplicity that it takes unit time to execute a strand, the work for the example dag in Figure 6-2 is 19. The *span*<sup>3</sup> of *A*, denoted by Span(A), is the length of the longest path of control dependencies in *A*. For computations that do not contain reducers, this is simply the longest path in User(A). Assuming unit-time strands, the span of the dag in Figure 6-2 is 10, which is realized by the path  $\langle 1, 2, 3, 6, 7, 8, 10, 11, 18, 19 \rangle$ . Work/span analysis is outlined in tutorial fashion in [11, Ch. 27] and [24].

Suppose that a program produces a dag *A* in time  $T_P(A)$  when run on *P* processors of an ideal parallel computer. We have the following two lower bounds on the execution time  $T_P(A)$ :

$$T_p(A) \geq \operatorname{Work}(A)/P$$

, (6.1)

$$T_P(A) \geq \operatorname{Span}(A)$$

. (6.2)

Inequality (6.1), which is called the *Work Law*, holds in this simple performance model, because each processor executes at most 1 instruction per unit time, and hence P processors can execute at most P instructions per unit time. Inequality (6.2), called the *Span Law*, holds because no execution that respects the partial order of the dag according to parallel-control dependencies can execute faster than the longest serial chain of instructions.

We define the *speedup* of a program as  $T_1(A)/T_P(A)$  — how much faster the *P*-processor execution is than the serial execution. Since all executions of a deterministic

<sup>&</sup>lt;sup>3</sup>The literature also uses the terms *depth* [4] and *critical-path length* [5].

program produce the same dag *A*, we have that  $T_1(A) = \text{Work}(A)$ , and  $T_{\infty}(A) = \text{Span}(A)$  (assuming no overhead for scheduling). Rewriting the Work Law, we obtain  $T_1(A)/T_P(A) \leq P$ , which is to say that the speedup on *P* processors can be at most *P*. If the application obtains speedup *P*, which is the best we can do in our model, we say that the application exhibits *linear speedup*. If the application obtains speedup greater than *P* (which cannot happen in our model due to the Work Law, but can happen in models that incorporate caching and other processor effects), we say that the application exhibits *superlinear speedup*.

The *parallelism* of the dag is defined as Work(A)/Span(A). For a deterministic computation, the parallelism is therefore  $T_1(A)/T_{\infty}(A)$ . The parallelism represents the maximum possible speedup on any number of processors, which follows from the Span Law, because  $T_1(A)/T_P(A) \le T_1(A)/\text{Span}(A) = \text{Work}(A)/\text{Span}(A)$ . For example, the parallelism of the dag in Figure 6-2 is 19/10 = 1.9, which means that any advantage gained by executing it with more than 2 processors is marginal, since the additional processors will surely be starved for work.

For a program that does not involve reducers, the dag model presented is sufficient for measuring the work and span of the computation. This model, however, does not represent any control dependencies involving runtime strands, although they do contribute to the span. In Chapter 7 we extend this model of computation to represent control dependencies involving runtime strands to portray their contribution to the work and span of a computation.

### Scheduling

A randomized "work-stealing" scheduler [1, 7], such as is provided by MIT Cilk and Cilk++, operates as follows. When the runtime system starts up, it allocates as many operating-system threads, called *workers*, as there are processors (although the programmer can override this default decision). Each worker's stack operates like a *deque*, or double-ended queue. When a subroutine is spawned, the subroutine's activation frame containing its local variables is pushed onto the bottom of the deque. When it returns, the frame is popped off the bottom. Thus, in the common case, the parallel code operates just like serial

code and imposes little overhead. When a worker runs out of work, however, it becomes a *thief* and "steals" the top frame from another *victim* worker's deque. In general, the worker operates on the bottom of the deque, and thieves steal from the top. This strategy has the great advantage that all communication and synchronization is incurred only when a worker runs out of work. If an application exhibits sufficient parallelism, stealing is infrequent, and thus the cost of bookkeeping, communication, and synchronization to effect a steal is negligible.

Work-stealing achieves good expected running time based on the work and span. In particular, if *A* is the executed dag on *P* processors, the expected execution time  $T_P(A)$  can be bounded as

$$T_P(A) \le \operatorname{Work}(A)/P + O(\operatorname{Span}(A)),$$

(6.3)

where we omit the notation for expectation for simplicity. This bound, which is proved in [7], assumes an ideal computer, but it includes scheduling overhead. For a deterministic computation, if the parallelism exceeds the number *P* of processors sufficiently, Inequality (6.3) guarantees near-linear speedup. Specifically, if  $P \ll \text{Work}(A)/\text{Span}(A)$ , then  $\text{Span}(A) \ll \text{Work}(A)/P$ , and hence Inequality (6.3) yields  $T_P(A) \approx \text{Work}(A)/P$ , and the speedup is  $T_1(A)/T_P(A) \approx P$ .

For a nondeterministic computation such as PBFS, however, the work of a *P*-processor execution may not readily be related to the serial running time. Thus, obtaining bounds on speedup can be more challenging. As Chapter 9 shows, however, PBFS achieves

$$T_P(A) \le \operatorname{Work}(\operatorname{User}(A))/P + O(\tau^2 \cdot \operatorname{Span}(\operatorname{User}(A))), \qquad (6.4)$$

where User(*A*) is the user dag of *A*,  $\tau$  is an upper bound on the time it takes to perform a REDUCE, which may be a function of the input size, and the work and span of User(*A*) are the sum of the lengths of the strands in *V*(User(*A*)) and the length of the longest path in User(*A*) respectively. (We shall formalize these concepts for computations with reducers in Chapters 7 and 8.) For nondeterministic computations satisfying Inequality (6.4), we define the *effective parallelism* as Work(User(*A*))/( $\tau^2 \cdot$  Span(User(*A*))). Just as with parallelism for deterministic computations, if the effective parallelism exceeds the number

*P* of processors by a sufficient margin, the *P*-processor execution is guaranteed to attain near-linear speedup over the serial execution.

Another relevant measure is the number of steals that occur during a computation. As is shown in [7], the expected number of steals incurred for a dag *A* produced by a *P*-processor execution is  $O(P \cdot \text{Span}(A))$ . This bound is important, since the number of REDUCE operations needed to combine reducer views is bounded by the number of steals.

## Chapter 7

## Reducers

This chapter reviews the definition of reducer hyperobjects from Frigo *et al.* [15] and extends the dag model to incorporate them. We first formalize the semantic definition of a reducer. We then examine how Cilk implements reducers, and we propose a modified locking protocol for managing views of a reducer within the runtime system. We shall clarify the notion of a user dag for a computation with reducers, and we shall define "performance dags," which include the strands that the runtime system implicitly invokes. Finally, we shall consider the inaccuracies in the performance dag representation of reducer operations, and we shall define a way to track the views of a reducer through a scheduling dag.

A reducer is defined in terms of an algebraic *monoid*: a triple  $(T, \otimes, e)$ , where *T* is a set and  $\otimes$  is an associative binary operation over *T* with identity *e*. From an object-oriented programming perspective, the set *T* is a base type which provides a member function RE-DUCE implementing the binary operator  $\otimes$  and a member function CREATE-IDENTITY that constructs an identity element of type *T*. The base type *T* also provides one or more UP-DATE functions, which modify an object of type *T*. In the case of bags, the REDUCE function is BAG-UNION, the CREATE-IDENTITY function is BAG-CREATE, and the UPDATE function is BAG-INSERT. As a practical matter, the REDUCE function need not actually be associative, although in that case, the programmer typically has some idea of "logical" associativity. Such is the case, for example, with bags. If we have three bags  $B_1$ ,  $B_2$ , and  $B_3$ , we do not care whether the bag data structures for  $(B_1 \cup B_2) \cup B_3$  and  $B_1 \cup (B_2 \cup B_3)$ are identical, only that they contain the same elements.

In order to analyze programs that use reducers with nonconstant-time REDUCE operations, we must address the non-trivial task of representing operations on reducers within our model of computation. In particular, although the dag model of computation presented in Chapter 6 represents the CREATE-IDENTITY and REDUCE operations that the runtime system performs implicitly, it does not model any parallel-control dependencies on these strands, and therefore it fails to model the effect of these operations on the work and span. Since the runtime system performs CREATE-IDENTITY and REDUCE operations nondeterministically during the computation, how they affect the work and span of the computation is not straightforward.

We shall address this problem as follows. First, we shall examine how the runtime system implements and manages reducers. We shall then clarify the definition of a user dag for computations with reducers and show how to augment this user dag to get a "performance dag" containing the implicit operations on reducers where we would like to charge for them. The model of reducers in the performance dag does not faithfully represent where these reducer operations are performed in the schedule, however, and in order to prove that the performance dag is sufficient for accounting for reducers, we need to examine a faithful representation of reducer operations. We shall therefore show how to account for reducer operations in the scheduling dag, and we shall use the scheduling-dag representation in Chapter 8 to prove that the performance dag suffices to account for operations on reducers.

### **Implementation of reducers**

To model and prove performance bounds on multithreaded computations with nonconstanttime reducers, we must first understand how the runtime system implements reducers. We also provide an alternative locking protocol to that proposed by Frigo *et al.* [15] for the runtime system to manage reducers, which guarantees that locks are held for constant time regardless of the runtime of any REDUCE operation.

First, we examine how the runtime system handles spawns and steals, as described in [15]. Every time a Cilk function is stolen, the runtime system creates a new *frame*.<sup>1</sup> Although frames are created and destroyed dynamically during a program execution, the

<sup>&</sup>lt;sup>1</sup>When we refer to frames in this paper, we specifically mean the "full" frames described in [15].

ones that exist always form a rooted tree. Each frame F provides storage for temporary values and local variables, as well as metadata for the function, including the following:

- a pointer *F*.*lp* to *F*'s left sibling, or if *F* is the first child, to *F*'s parent;

- a pointer *F*.*c* to *F*'s first child;

- a pointer *F*.*r* to *F*'s right sibling.

These pointers form a left-child right-sibling representation of the part of this tree that is distributed among processors, which is known as the *steal tree*.

To handle reducers, each worker in the runtime system uses a hash table called a *hypermap* to map reducers into its local views. To allow for lock-free access to the hypermap of a frame F while siblings and children of the frame are terminating, F stores three hypermaps, denoted F.hu, F.hr, and F.hc. The F.hu hypermap is used to look up reducers for the user's program, while the F.hr and F.hc hypermaps store the accumulated values of F's terminated right siblings and terminated children, respectively.

When a frame is initially created, its hypermaps are empty. If a worker using a frame F executes an UPDATE operation on a reducer h, the worker tries to obtain h's current view from the F. hu hypermap. If h's view is empty, the worker performs a CREATE-IDENTITY operation to create an identity view of h in F. hu.

When a worker returns from a spawn, first it must perform up to two REDUCE operations to reduce its hypermaps into its neighboring frames, and then it must *eliminate* its current frame. To perform these REDUCE operations and elimination without races, the worker grabs locks on its neighboring frames. The algorithm by Frigo *et al.* [15] uses an intricate protocol to avoid long waits on locks, but the analysis of its performance assumes that each REDUCE takes only constant time.

To support nonconstant-time REDUCE functions, we modify the locking protocol. To eliminate a frame *F*, the worker first reduces  $F.hu \otimes = F.hr$ . Second, the worker reduces *F.lp.hc*  $\otimes = F.hu$  or *F.lp.hr*  $\otimes = F.hu$ , depending on whether *F* is a first child.

Workers eliminating F.lp and F.r might race with the elimination of F. To resolve these races, Frigo *et al.* describe how to acquire an "abstract lock" between F and these neighbors, where an *abstract lock* is a pair of locks that correspond to an edge in the steal tree. We use these abstract locks to eliminate a frame F according to the locking protocol

| 1  | while TRUE                                                                    |

|----|-------------------------------------------------------------------------------|

| 2  | Acquire the abstract locks for edges $(F, F. lp)$ and $(F, F. r)$ in an order |

|    | chosen uniformly at random                                                    |

| 3  | if $F$ is a first child                                                       |

| 4  | L = F.lp.hc                                                                   |

| 5  | else $L = F.lp.hr$                                                            |

| 6  | R = F.hr                                                                      |

| 7  | if $L == \emptyset$ and $R == \emptyset$                                      |

| 8  | if $F$ is a first child                                                       |

| 9  | F.lp.hc = F.hu                                                                |

| 10 | else $F.lp.hr = F.hu$                                                         |

| 11 | Eliminate F                                                                   |

| 12 | break                                                                         |

| 13 | R' = R; L' = L                                                                |

| 14 | $R = \emptyset; L = \emptyset$                                                |

| 15 | Release the abstract locks                                                    |

| 16 | for each reducer $h \in R'$                                                   |

| 17 | if $h \in F.hu$                                                               |

| 18 | $F.hu(h) \otimes = R'(h)$                                                     |

| 19 | else $F.hu(h) = R'(h)$                                                        |

| 20 | for each reducer $h \in L'$                                                   |

| 21 | if $h \in F.hu$                                                               |

| 22 | $F.hu(h) = L'(h) \otimes F.hu(h)$                                             |

| 23 | else $F.hu(h) = L'(h)$                                                        |

| 24 |                                                                               |

**Figure 7-1:** A modified locking protocol for eliminating a frame F containing reducers with nonconstant-time REDUCE operations. This locking protocol guarantees that locks are held for O(1) time, regardless of the running time of any REDUCE operation.

shown in Figure 7-1.

### **Modeling reducers**

To specify the nondeterministic behavior encapsulated by reducers precisely, consider a computation A of a multithreaded program, where V(A) be the set of executed strands. We assume that the implicitly invoked functions for a reducer — REDUCE and CREATE-IDENTITY — execute only serial code. We model each execution of one of these functions as a single strand containing the instructions of the function. If an UPDATE causes the runtime system to invoke CREATE-IDENTITY implicitly, the serial code arising from UPDATE

is broken into two strands sandwiching the point where CREATE-IDENTITY is invoked. We can partition V(A) into three classes of strands:

- $V_{v}$ : User strands arising from the execution of code explicitly invoked by the programmer, including calls to UPDATE.

- $V_t$ : *Init strands* arising from the execution of CREATE-IDENTITY when invoked implicitly by the runtime system, which occur when the user program attempts to update a reducer, but a local view has not yet been created.

- $V_{\rho}$ : *Reduce strands* arising from the execution of REDUCE, which occur implicitly when the runtime system combines views.

Notice that  $V_1 \cup V_p$  is the set of runtime strands in V(A), as Chapter 6 mentions.

Since, from the programmer's perspective, the runtime strands are invoked "invisibly" by the runtime system, his or her understanding of the program generally relies only on the user strands. We therefore maintain the definition of the user dag exactly as it was in Chapter 6. For a computation A, we set  $V(\text{User}(A)) = V_{\upsilon}$ , and we set  $E(\text{User}(A)) = E_{\chi}$ . If A involves reducers, then the user dag omits all runtime strands in A. For example, the user dag associated with the computation in Figure 6-1 looks exactly like the dag shown in Figure 6-2. The work of User(A) is the sum of the lengths of the strands in V(User(A)), and the span of User(A) is the length of the longest path through User(A).

To track the views of a reducer *h* in the user dag, let h(v) denote the view of *h* seen by a strand  $v \in V(\text{User}(A))$ . The runtime system maintains the following invariants:

- **Invariant 2.** If  $u \in V(\text{User}(A))$  has out-degree 1 and  $(u, v) \in E(\text{User}(A))$ , then h(v) = h(u).

- **Invariant 3.** Suppose that  $u \in V(\text{User}(A))$  is a spawn strand with outgoing edges  $(u,v), (u,w) \in E(\text{User}(A))$ , where  $v \in V(\text{User}(A))$  is the first strand of the spawned subroutine and  $w \in V(\text{User}(A))$  is the continuation in the parent. Then, we have h(v) = h(u) and

$$h(w) = \begin{cases} h(u) & \text{if } w \text{ was not stolen;} \\ \text{new view otherwise.} \end{cases}$$

**Invariant 4.** If  $v \in V(\text{User}(A))$  is a sync strand, then h(v) = h(u), where *u* is the first strand of *v*'s function.

When a new view h(w) is created, as is inferred by Invariant 3, we say that the old view h(u) *dominates* h(w), which we denote by h(u) > h(w). For a set H of views, we say that two views  $h_1, h_2 \in H$ , where  $h_1 > h_2$ , are *adjacent* if there does not exist  $h_3 \in H$  such that  $h_1 > h_3 > h_2$ . We can define the *dominates function* dom  $\{h_1, h_2, ..., h_k\}$  to be the view  $h_i \in \{h_1, h_2, ..., h_k\}$  such that for all  $j \in \{1, 2, ..., k\}$ , if  $j \neq i$  then  $h_i > h_j$ .

A useful property of sync strands is that the views of strands entering a sync strand  $v \in V(\text{User}(A))$  are totally ordered by the dominates relation. That is, if k strands each have an edge in E(User(A)) to the same sync strand  $v \in V(\text{User}(A))$ , then the strands can be numbered  $u_1, u_2, \ldots, u_k \in V(\text{User}(A))$  such that  $h(u_1) \ge h(u_2) \ge \cdots \ge h(u_k)$ . Moreover, we have  $h(u_1) = h(v) = h(u)$ , where u is the first strand of v's function. These properties can be proved inductively, noting that the views of the first and last strands of a function must be identical, because a function implicitly syncs before it returns. The runtime system always reduces adjacent pairs of views in this ordering, destroying the dominated view in the pair.

If a computation A does not involve any runtime strands, the "delay-sequence" argument in [7] can be applied to User(A) to bound the P-processor execution time:  $T_P(A) \leq$  Work(User(A))/P+O(Span(User(A))). Chapter 8 applies a similar delay-sequence argument to computations containing runtime strands. To do so, we augment User(A) with the runtime strands to produce a *performance dag* Perf(A) for the computation A, where

- $V(\operatorname{Perf}(A)) = V(A) = V_{\upsilon} \cup V_{\iota} \cup V_{\rho}$ ,

- $E(\operatorname{Perf}(A)) = E_{\upsilon} \cup E_{\iota} \cup E_{\rho}$ ,

where the edge sets  $E_1$  and  $E_{\rho}$  are constructed as follows.

The edges in  $E_1$  are created in pairs. For each init strand  $v \in V_1$ , we include (u, v) and (v, w) in  $E_1$ , where  $u, w \in V_0$  are the two strands comprising the instructions of the UPDATE whose execution caused the invocation of the CREATE-IDENTITY corresponding to v.

The edges in  $E_{\rho}$  are created in groups corresponding to the set of REDUCE functions that must execute before a given sync. Suppose that  $v \in V_{v}$  is a sync strand, that k strands

$u_1, u_2, \ldots, u_k \in V_{\upsilon}$  join at *v*, and that k' < k reduce strands  $r_1, r_2, \ldots, r_{k'} \in V_{\rho}$  execute before the sync. Consider the set  $U = \{u_1, u_2, \ldots, u_k\}$ , and let  $h(U) = \{h(u_1), h(u_2), \ldots, h(u_k)\}$  be the set of k' + 1 views that must be reduced. Construct a *reduce tree* as follows:

1 while  $|h(U)| \ge 2$

Let r ∈ {r<sub>1</sub>, r<sub>2</sub>,..., r<sub>k'</sub>} be the reduce strand that reduces a "minimal" pair h<sub>j</sub>, h<sub>j+1</sub> ∈ h(U) of adjacent strands, meaning that if a distinct r' ∈ {r<sub>1</sub>, r<sub>2</sub>,..., r<sub>k'</sub>} reduces adjacent strands h<sub>i</sub>, h<sub>i+1</sub> ∈ h(U), we have h<sub>i</sub> > h<sub>j</sub>

Let U<sub>r</sub> = {u ∈ U : h(u) = h<sub>j</sub> or h(u) = h<sub>j+1</sub>}

4 Include in  $E_{\rho}$  the edges in the set  $\{(u, r) : u \in U_r\}$

5

$$U = U - U_r \cup \{r\}$$

6 Include in  $E_{\rho}$  the edges in the set  $\{(r, v) : r \in U\}$

Since the reduce trees and init strands only add more dependencies between strands in the user dag User(A) that are already in series, the performance dag Perf(A) is indeed a dag. The work of Perf(A) is the sum of the lengths of all the strands in Perf(A). Since we shall consider all the edges in E(Perf(A)) to be control dependencies, the span of Perf(A) is the length of the longest path in Perf(A). Chapter 8 proves that we can use the longest path in Perf(A) to bound the running time of a computation A that contains reducers.

The edges in a performance dag reflect the guarantees that the runtime system makes on when runtime strands occur relative to user strands in a schedule of the computation. Consequently, for a computation A involving reducers, we have two invariants that relate User(A) and Perf(A) to Sched(A), which are similar to Invariant 1.

- **Invariant 5.** If a user strand  $u \in \text{User}(V)$  precedes a strand  $v \in V(A)$  in User(A), then u precedes v in Sched(A).

- **Invariant 6.** If a strand  $u \in V(A)$  precedes a sync strand  $v \in V(A)$  in Perf(A), then u precedes v in Sched(A).

### Faithfully representing REDUCE operations

Although the performance dag is useful for bounding the work and span of computations with reducers, it does not faithfully model when reduce strands occur within the computa-

**Figure 7-2:** A dag representation of a computation with a REDUCE operation executed opportunistically. The set of strands and the set of straight edges represent the performance dag of the computation. In particular, the numbered, dark-colored vertices represent user and init strands within the computation, and each dark-colored vertex labeled with "…" represents a sequence of user and init strands. The gray vertices labeled R1 and R2 represent reduce operations where they are placed in the performance dag. The lighter-gray vertex labeled R2 and connected via curved arrows represents the position of R2 as dictated by scheduling dependencies only.